CISC und RISC - Die Gegensätze der Rechnerarchitekturen

Von Bernd Leitenberger

Was bedeuten die Abkürzungen?

RISC und CISC stehen für die Begriffe "Reduced Instruction Set Computer", bzw.

"Complex Instruction Set Computer". Damit sind zwei grundsätzliche Philosophien im Computerbau gemeint.

Computer sind heute meistens keine reinen RISC- oder CISC-Maschinen, sondern haben von

beiden etwas übernommen.

CISC - die natürliche Evolution

Bei den Begriffen geht es darum, wie die CPU eines Computers arbeitet. Bei dem CISC-Modell hat die CPU üblicherweise wenige Register (Speicherplätze in der CPU), wovon manche auch meist Spezialaufgaben haben. Dazu finden sich viele Befehle,

darunter auch sehr mächtige, die z. Bsp. in einer Schleife gleich mehrere Register bearbeiten. Die Befehle haben meist ungleiche

Befehlslängen. Die häufigsten benutzten nur ein Byte, weniger häufige zwei oder drei Bytes. Dadurch kann der Code

kompakt gehalten werden.

Wenn eine CPU weiterentwickelt wird, kommt es oft vor, daß sie immer mehr in Richtung CISC wandert. Der Grund ist relativ

einfach. Man kann immer mehr Transistoren auf einem Chip zu integrieren. So hatte die

erste "8086"-CPU 29.000 Transistoren und ein Pentium IV verfügt über 42

Millionen Transistoren. Diese Möglichkeit wird fast immer genutzt, um neue Befehle zu integrieren, die

z. Bsp. das Programmieren erleichtern. Dadurch wird aber das gesamte Design komplexer.

(...)

Auch bei den Großrechnern früherer Tage war oft die CISC-Architektur

vorherrschend: Man war der Überzeugung, je "mächtiger" die Befehle einer CPU sind, um so schneller

sind diese und um so weniger Speicherplatz benötigt der Code. Ein prinzipieller

Nachteil von CISC ist, daß es in der Regel nicht möglich ist, viele Register zu verwenden. Register sind Speicherplätze in der CPU

und damit der schnellste Speicher den eine CPU adressieren kann. Die kleine Anzahl liegt daran,

daß bei den meisten Befehlen auch das Register auf das er wirkt, mit einkodiert wird. Je mehr Register man hat, desto weniger Befehle kann man realisieren. Sehr oft gab

es dann Zwischenlösungen, wie z. Bsp. Befehle, die nur mit bestimmten Registern arbeiteten.

RISC - Reduziert auf Geschwindigkeit

RISC geht einen anderen Weg. Man beschränkt sich auf die wirklich notwendigen Befehle. Als Ausgleich

gibt es erheblich mehr Register (bis zu 256) auf dem Chip, so daß man viel öfter schnelle Register-Register-Operationen hat, als langsame

Speicher-Register-Operationen. Die wenigen Befehle machen das Design einfacher und man kann den Prozessor billiger

herstellen. Gleichzeitig wird das Datenformat vereinheitlicht. Bei RISC haben alle Befehle eine einheitliche Länge, wodurch das

Dekodieren schneller geht, aber

der Code zwangsläufig größer ist.

CISC oder RISC - Der Kampf der Heimcomputer

Das historische Duell fing 1975 zwischen dem "8080" und dem "6502" an und sollte sich über 10 Jahre hinziehen.

Beide Architekturen waren erfolgreich, obwohl Sie nicht verschiedener hätten sein können. Der

"8080" war schon ein typischer CISC-Vertreter.

Der "8080" hatte einen Akkumulator (A) und

sechs 8 Bit-Register (B,C,D,E,H,L), die zusammen zu 16

Bit-Registern (BC, DE, HL) geschaltet werden konnten.

Dazu kam der 16 Bit-Stackpointer und der Programmzähler.

Speicheroperationen gingen beim "8080" nur übers HL Register, dafür bot dieses

auch 16 Bit-Operationen wie Addition und Subtraktion. Der

"Z80" erweiterte das

Design des "8080". Er führte einen zweiten Registersatz ein, dazu zwei neue

Register IX und IY, die für Indexoperationen benutzt wurden. Die BC- und DE-Register wurden genauso tauglich wie das

HL-Register für Speicheroperationen und 16 Bit-Rechnungen, dazu kamen eine Fülle von Befehlen:

Blockoperationen, In/Out, Bitweise Rotation / Verschiebung. Aus den 57 Befehlen des

"8080" machte der "Z80" über 600! Das kostete aber Zeit beim Dekodieren. Ein Befehl konnte zwischen einem und 5 Byte lang sein. Die Ausführung dauerte zwischen 4 und 28

Takte.

Wie einfach war dagegen das Design des

"6502", nur drei Register à 8 Bit, sogar nur

ein 8 Bit-Stackpointer. Der Stack lag fest zwischen Adresse 256 und 511 und über die Indexregister konnte man die Adressen 0

bis 255 ansprechen (und darüber das restliche RAM). Man konnte aber diese 256 Byte RAM auch als 256 zusätzliche Register

ansehen, denn bei Erscheinen des "6502" waren die RAM's schneller als Mikroprozessoren. Zudem waren die Befehle schnell zu

dekodieren (in 1-2 Takten), da der "6502" sowohl aufsteigende wie absteigende Flanke des Taktsignales nutzte (so konnte man die

Taktfrequenz im Vergleich zu einem "8080" oder "Z80" schon halbieren).

So verschieden die Designs waren, in der Realität waren beide erfolgreich. Zwar war der

"6502" bei gleicher Taktfrequenz schneller als ein "Z80", aber das glich sich dadurch aus,

daß dieser meist zwischen 1-2 MHz lief, während der "Z80" 3-4

MHz aufwies. Ab 1983 wurden noch schnellere

"Z80"-Versionen herausgebracht, die bis 10 MHz gingen. Diese Entwicklung war beim

"6502" nicht möglich, da er zwingend auf das schnelle RAM angewiesen war. Dafür war ein

"6502" immer ein Stück preiswerter, weil er einfacher herzustellen war.

Der wohl radikalste Ansatz von RISC im 8 Bit Zeitalter war der relativ selten eingesetzte

RCA "1802". Der Prozessor war mit nur 16 Befehlen

ausgestattet, lief dafür schon 1975 mit 6 MHz, während der

"6502" mit einem und der "8080" mit 2,5 MHz eingeführt wurden. Er spielte auf dem Heimcomputermarkt keine Rolle, steckt dafür aber in zahlreichen

Raumsonden, da er technisch sehr robust und wenig anfällig gegenüber statischer Elektrizität war.

Intel und der IBM PC

Der Intel "8086" ist ebenfalls ein typischer Vertreter von CISC. Er wurde im

"IBM PC" verwendetet. Die Rechenleistung der x86-Architektur galt spätestens ab

1986 als das Maß aller Dinge. Grund für das CISC-Design war, daß man, um Entwicklungskosten und

Zeit zu sparen, das "8080"-Design aufgebläht hatte. Dadurch hatte der x86 einige Macken,

die seine Architektur komplex machten. Die wichtigste war, daß er direkt nur 3 Segmente

(Code, Daten und Stack) à 64 KB ansprechen konnte. Diese Fenster wurden in einem

Adreßraum von 1 MB verschoben. Als man

mit dem 286er die Architektur auf volle 16 MB Adreßraum erweiterte und

später mit dem 386er sogar auf 4 GB bei 32 Bit, blieb die alte "Real Mode" als zusätzlicher

Modus immer noch erhalten. Zudem konnte man nicht einfach neue Register einführen, obwohl der Befehlssatz der x86-Serie im Laufe der Zeit erweitert wurde.

(...)

Die Renaissance von RISC

Nun änderte sich aber auch in der Programmierung bis Mitte der 80er Jahre etwas. Bis zum

"8086", mit seiner begrenzten Rechenleistung und kleinem Speicher, war es nötig, für

schnelle Programme in Assembler zu programmieren. Bei der Einführung des viermal schnelleren 286er

samt mehr Speicher, gewannen aber Programme die mit Hochsprachen wie C entwickelt wurden

immer mehr Bedeutung und Assembler wurde auf kleine systemnahe Routinen beschränkt. Nun ergaben aber Untersuchungen,

daß Compiler weitaus weniger als der menschliche Programmierer den Befehlssatz eines Prozessors ausschöpften. 80% des

Compilercodes verwendeten nur 20% der Befehle, ja bestimmte Befehle wurden überhaupt nicht verwendet. Dies liegt daran,

daß Compiler ein sehr starres Muster haben. Mehr noch, viele Vorteile von CISC, mächtige Befehle, die nur mit einem bestimmten

Register arbeiteten, wurden oft gar nicht genutzt. Dies liegt auch am starren Vorgehen eines

Compilers. Dieser hat nicht mehrere Codealternativen vorrätig, sondern eben nur eine Version und verwendet dazu idealerweise die Befehle, die mit allen Registern arbeiten.

Dies war die Renaissance von RISC. Ende der 80er Jahre bauten nahezu alle Hersteller RISC-Prozessoren.

Die gemeinsamen Merkmale waren: Wenige, schnell zu dekodierende Befehle, einheitliches Befehlsformat und schnelle Dekodierung. Die

einzelnen Konzepte waren durchaus unterschiedlich. RISC war auch eine Möglichkeit, mit relativ wenigen Transistoren eine sehr hohe Rechenleistung zu erreichen. Dies war wichtig für Hersteller denen im Prozessormarkt von Intel immer mehr Marktanteile entzogen wurden. Motorola

schuf zusammen mit Apple und IBM den

"Power PC Chip". Der Chip hatte dadurch sehr

unterschiedliche Anforderungen zu erfüllen: Apple und Motorola wollten einen Nachfolger für die in die Jahre gekommene

"68000"-Serie, so konnte dieser deren Befehle emulieren. IBM wollte aber

gleichzeitig einen schnellen Prozessor für Minicomputer und sogar

Großrechner. Der "Power PC" ist sehr erfolgreich und hat seit 1993 schon die vierte Generation erlebt. Erst mit dieser ist die Einführung eines Passivkühlers notwendig

geworden, bei sonst ähnlicher Rechenleistung wie ein Pentium-Pendant (aber immer etwas niedrigerem Takt).

Eine traurige Rolle spielte der "ARM"-Prozessor. Die meisten neuen RISC-Prozessoren

waren für Workstations gedacht. Doch Acorn, eine in England bekannte

Firma, brachte 1988 einen PC mit diesem Prozessor heraus, der es mit einem

386er aufnehmen konnte- zu einem Bruchteil der Kosten. Doch es fehlte der

Firma an Bekanntheit, um dieses Gerät, den "Archimedes", zu etablieren. ARM

hat die Zeichen der Zeit erkannt und den "ARM"- Prozessor als Microcontroller

erfolgreich gemacht. "ARM"-Prozessoren haben im 32 Bit- Mikrocontroller-Bereich einen Marktanteil von 70% und werden in Lizenz von zahlreichen

Unternehmen, sogar von Intel, gefertigt.

Sun läutete mit der "Sun 4" und dem

"SPARC"-Prozessor 1987 als erste Firma

den Wechsel ein. Der "SPARC" hatte in der ersten Version nur 55.000

Transistoren, aber eine höhere Geschwindigkeit als ein 386er mit 275.000

Transistoren. Spezielle Features machten vor allem die Hochsprachenprogrammierung auf diesem Prozessor schnell. Bald zogen

andere Workstation-Hersteller wie MIPS oder DEC mit ihrem "Alpha", der

bis heute die Krone in der Geschwindigkeit hält, nach.

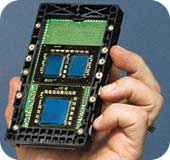

Eine Besonderheit waren die Transputer-Prozessoren von

INMOS. Mehrere dieser Prozessoren konnten zusammengeschaltet werden und parallel an einem Problem arbeiten. Die Abbildung der zeitgleich

erschienenen Prozessoren "Intel 80386" und "INMOS T400" zeigt auf dem Prozessor

die Unterschiede zwischen CISC und RISC:

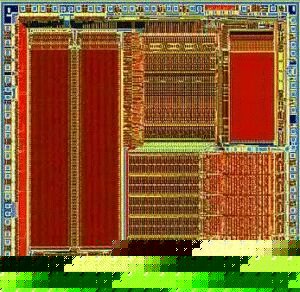

Große, gleichförmige Felder beim

"T400" mit viel interen Registern und 1 KB Cache on Board:

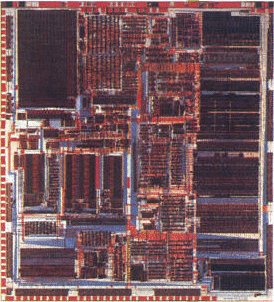

"Rauh" wirkende Felder beim

"80386" mit Logikfunktionen, die erheblich mehr Transtistoren

erfordern:

Der "INMOS T400" war trotz geringerer Integrationsdichte

schneller als der "80386".

Wodurch wird RISC schnell?

Nun, dazu muß man wissen wie ein Befehl von einem Mikroprozessor ausgeführt wird. Jeder Prozessor hat mindestens 4

elementare Operationen pro Befehl auszuführen:

-

Daten vom Speicher holen.

-

Daten dekodieren, d. h. feststellen, was für ein Befehl gemeint ist.

-

Befehl ausführen.

-

Daten in Register / Speicher zurückschreiben.

Für jede Stufe braucht ein Prozessor mindestens einen Taktzyklus, meistens aber

mehrere. Nun gibt es hier einige Dinge die wichtig sind:

-

Die Daten vom Speicher zu holen

benötigt Zeit. Speicherbausteine sind langsam im Vergleich zu einem Prozessor.

-

Je mehr und je komplexere Befehle ein Prozessor hat, desto länger dauert das Dekodieren

CISC-Prozessoren haben nun folgende Strategie: Das Dekodieren dauert hier länger, da der Code kein einheitliches Format hat,

dafür aber sehr kurz ist (geringerer Speicherzugriff). Als Ausgleich können die Befehle mehr, so das weniger ausgeführt werden

müssen. Viele Register sind, wegen der Forderung nach kurzem Code, nicht möglich. Die komplexen Befehle werden im Chip in

einfachere Instruktionen zerlegt. Dafür gibt es Microcode- ein ROM auf dem Chip.

(...)

RISC versucht die Speicherzugriffe auf zwei Weisen zu minimieren:

-

Viele Register. Die Daten können in diesen gehalten werden.

Bei den meisten Befehlen fallen die Angaben von Speicheradressen weg.

Idealerweise gibt es nur einen Befehl der direkt mit dem Speicher

kommuniziert- einen Lade- und Speicherbefehl. Alle anderen Befehle arbeiten mit Registern und sind

dementsprechend schnell. Als weiteren Vorteil entfallen die zusätzlichen Zyklen für einen Speicherzugriff.

RISC-Prozessoren verfügen je nach Typ zwischen 32 und 256 Registern, die universell benutzt werden können. CISC-Typen, wie

der Motorola "680x0" oder Intel "80x86", haben 16 bzw. 12 Register.

(...)

CISC-Prozessoren müssen sich viel einfallen lassen, um die verschiedenen

Kombinationsmöglichkeiten in einer Pipeline zu dekodieren. Die Pipelines sind dort lang,

weil es so viele Möglichkeiten gibt und man deswegen mehr Stufen benötigt. RISC-Prozessoren wissen dagegen genau, wo der nächste Befehl beginnt und können mehr automatisieren. Die Pipeline ist kürzer. Das

ist von Vorteil, wenn ein Sprung im Programm kommt, denn dann stimmen alle Daten in der Pipeline nicht mehr.

Die Forderung nach einfachen Befehlen erwächst auch hieraus: Das schnelle Dekodieren der Befehle im

"Fließband" hat nur einen Vorteil, wenn auch die Befehle schnell ausgeführt werden, denn sonst hat man nichts von dem Geschwindigkeitsvorteil.

Daher gibt es nur elementare Befehle, die idealerweise in einem Takt ausgeführt werden.

Intel's Sieg - Ein CISC Sieg?

Selbst INTEL brachte 1989 einen RISC-Prozessor heraus, den

"Intel 860". Doch bei Intel waren Kunden nicht bereit, sich vom

althergebrachten PC-Standard zu lösen. Mitte der 90er Jahre hatte Intel seine x86-Reihe soweit gesteigert,

daß er nun auch mit Multiprozessorsystemen in den Markt der RISC-beherrschten Workstations eindrang. Dank Rückgriff auf PC-Hardware waren diese

deutlich billiger herzustellen. Nun rächte es sich, daß Hersteller wie Sun, Silicon Graphics oder DEC den PC-Markt nie beachteten.

Als dann etwa zur gleichen Zeit auch vermehrt Netzwerke ihren Einzug in Firmen hielten,

blieben die Kunden, die bisher PC's hatten, auch bei dem was sie kannten: Server mit x86-Hardware und

"Windows NT", anstatt Workstations und "UNIX".

Den Endverbraucher interessiert das "was hinten rauskommt", um einen Bundeskanzler zu zitieren. Was nützt es, wenn ein Power-PC mit 450

MHz und passivem Kühler genauso schnell ist, wie ein Pentium III

mit 700 MHz und aufwendigem Kühler? Solange ein PC billiger als ein Mac ist, weil er viel häufiger hergestellt wird, geht die Rechnung zugunsten des PC auf. Und Intels Prozessoren können

mithalten. Anstatt den Prozessorcode zu verändern, steigerte man

die Taktfrequenz, integrierte L1- und L2-Cache in den Kern, um die Geschwindigkeit zu steigern.

Cisc hat also gesiegt- oder?

Nein! Zum einen gibt es zahlenmäßig erheblich mehr RISC- als CISC-Prozessoren. Denn zum Einsatz kommen Sie überall dort, wo keine IBM-Kompatibilität verlangt wird: Als

Druckercontroller, in PDA's (wegen dem Stromverbrauch), in den Spielkonsolen und

in

zahllosen Elektronikbauteilen im Auto (Ein Mittelklassewagen besitzt zwischen 13 und 30 Mikroprozessoren, die meisten als

"Embedded Controller").

Zum andern gibt es heute die Trennung CISC und RISC nicht mehr. Intels erster 64 Bit- Prozessor

"Itanium" hat Anleihen an RISC gemacht. Die RISC-Prozessoren wurden mit der Weiterentwicklung auch komplexer und nähern sich CISC.

Schlußendlich aber gibt es die CISC-Architektur des x86 Prozessors nicht mehr...

Bei Intel hat sich seit dem 486er einiges getan. Der 486er kam 1989 raus und zeigte, daß die x86-Architektur so langsam am Ende war.

Durch eine 5-stufige Pipeline konnte man nun 80% der Befehle in einem Taktzyklus

ausführen- schneller ging es mit der x86-Architektur nicht, trotzdem war der 486er nur ca. 60% schneller als ein 386er und lange Zeit zu teuer. Erst

1993 konnten die Verkäufe

die des 386er überflügeln, wobei Intel noch geärgert haben dürfte,

daß vorher AMD mit der 40 MHz-Version des 386er (Intel hatte nur

eine 33 MHz-Version), das große Geschäft machte.

Kurzum: Der 486er- Nachfolger "Pentium" mußte kompatibel und neu sein. Was Intel machte, war folgendes: Nach dem

Dekodieren der Befehle, werden diese in einfachere RISC-Befehle übersetzt, umgruppiert und zwei Rechenwerken die reine RISC-Maschinen sind, zugeführt. Seit dem

"Pentium Pro" ist dies so, und ein "Pentium IV" ist im Prinzip ein guter x86-Emulator. Eine x86-Instruktion kann dabei

eine, aber auch 3 oder 4 einfache RISC-Operationen umfassen. Dabei sind diese relativ lang, beim

"Pentium III" 118 Bit. Beim "Pentium IV" wahrscheinlich nur etwa die Hälfte.

(...)

Mit dem neuen 64 Bit "Itanium"-Prozessor wird auch bei Intel eine RISC-Einheit mit 128 Registern einziehen.

Der neue 64 Bit-Modus ist eine richtige RISC-Architektur mit

konstanter Befehlsbreite von 41 Bit, wobei zur Optimierung 3 Befehle zu einem 128

Bit-Doppelwort zusammengefaßt werden- der Compiler, und nicht der Prozessor, soll in den verbleibenden 5

Bit's Informationen über die Abhängigkeit der Befehle speichern. Dadurch will man die aufwendige spekulative Ausführung und Umgruppierung der

x86-Serie erleichtern.

(...)

Kontakt: www.bernd-leitenberger.de

Zurück